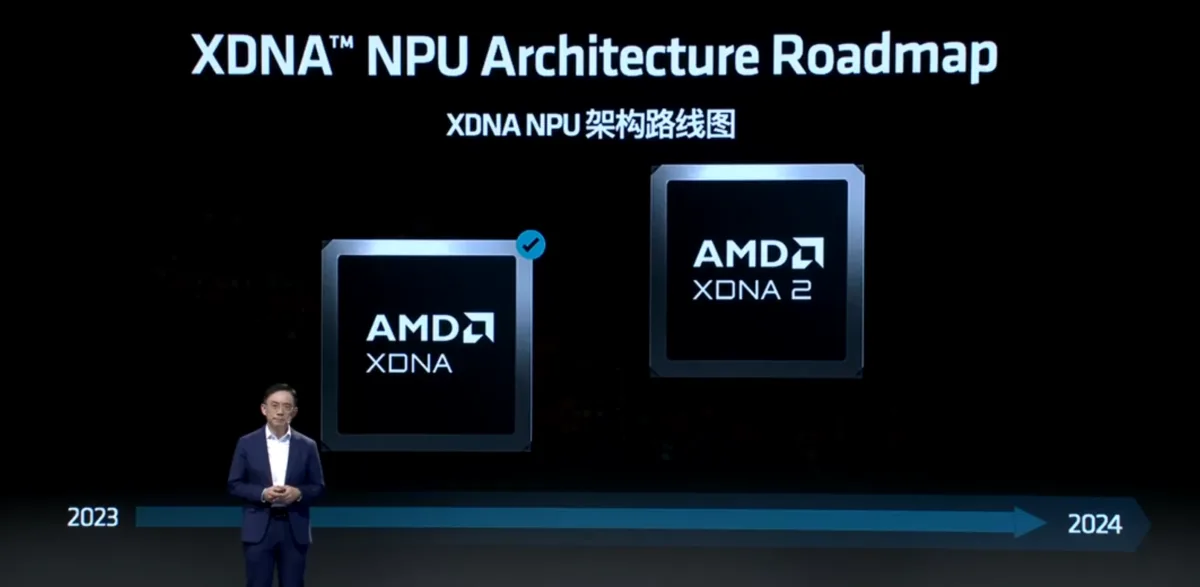

A AMD, em janeiro de 2024, lançou o driver open-source XDNA para o kernel Linux, com o objetivo de suportar as NPUs Ryzen AI presentes em seus processadores. Essas unidades de processamento neural (NPUs) são projetadas para acelerar tarefas de inferência de IA, como redes neurais convolucionais (CNNs) e modelos de linguagem (LLMs), tornando a execução de aplicações de aprendizado de máquina mais eficiente. O driver é baseado no subsistema de aceleração do Linux e utiliza a arquitetura AMD XDNA.

Após o início do processo de revisão formal em julho, a AMD publicou na última sexta-feira (11 de outubro) a quarta versão dos patches para o driver XDNA, trazendo melhorias significativas com base em revisões anteriores. Entre as mudanças está a remoção de códigos de buffer de depuração e outras correções. A expectativa é que essa nova versão dos patches esteja próxima de ser aceita no kernel principal.

Com o lançamento da série AMD Ryzen 7040 em meados de 2023, ainda é preocupante que o driver XDNA não tenha sido incluído no kernel principal, considerando que essas NPUs estão presentes em laptops há mais de um ano. Se esta quarta rodada de revisões for bem-sucedida, o driver poderá ser mesclado na janela de fusão do Linux v6.13, prevista para ocorrer entre novembro e dezembro. No entanto, a versão estável do Linux 6.13 só estará disponível em fevereiro de 2025. Portanto, usuários de distribuições como o Ubuntu só devem ver suporte nativo às NPUs Ryzen AI na versão 25.04 ou em distribuições similares, o que atrasaria o suporte em quase dois anos após o lançamento das NPUs da AMD nos dispositivos móveis.

Além do kernel driver, há a integração de uma pilha de suporte em espaço de usuário, incluindo o XRT (Xilinx Runtime) e o plugin AMD AIE IREE, que complementam o funcionamento das NPUs. O firmware necessário para as NPUs já está disponível no repositório de firmware DRM.

Os interessados podem conferir os novos patches da versão 4 na lista dri-devel, onde a AMD também detalhou outros componentes críticos da NPU, como os processadores de IA em matriz, o microcontrolador responsável pela execução do firmware e o controle do dispositivo via PCI Express. A NPU é equipada com um mecanismo de tradução de endereços, garantindo acesso seguro à memória do host, e também oferece suporte a múltiplos contextos de execução simultâneos e isolados.