O DRAM de 16 Kbit é um tipo de memória de acesso aleatório dinâmico que foi desenvolvido na década de 1970 e usado em vários dispositivos eletrônicos, como computadores, consoles de videogame e calculadoras. O DRAM de 16 Kbit tem uma capacidade de armazenamento de 16.384 bits, o que equivale a 2.048 bytes ou 2 kilobytes.

O DRAM de 16 Kbit é composto por uma matriz de células de memória, cada uma contendo um transistor e um capacitor. O transistor atua como um interruptor que permite ou impede a passagem de corrente elétrica para o capacitor, que armazena um bit de informação (0 ou 1) dependendo da sua carga elétrica. O DRAM de 16 Kbit tem uma organização de 128 linhas por 128 colunas, totalizando 16.384 células.

Para acessar os dados armazenados no DRAM de 16 Kbit, é preciso fornecer um endereço de memória, que é dividido em duas partes: o endereço da linha e o endereço da coluna. O endereço da linha é usado para selecionar uma das 128 linhas da matriz, ativando o transistor de cada célula dessa linha. O endereço da coluna é usado para selecionar uma das 128 colunas da matriz, lendo ou escrevendo o bit armazenado no capacitor da célula correspondente.

Uma das características do DRAM de 16 Kbit é que ele precisa ser constantemente atualizado para manter os dados armazenados. Isso ocorre porque os capacitores tendem a perder a carga elétrica com o tempo, causando a alteração ou perda dos bits. Para evitar isso, o DRAM de 16 Kbit tem um circuito integrado que realiza ciclos de atualização periódicos, lendo e reescrevendo os bits de cada célula.

O DRAM de 16 Kbit foi um avanço tecnológico na época, pois permitiu aumentar a capacidade e reduzir o custo e o tamanho das memórias. No entanto, com o desenvolvimento de novas tecnologias, o DRAM de 16 Kbit foi sendo substituído por versões mais rápidas, eficientes e compactas, como o DRAM de 64 Kbit, o DRAM de 256 Kbit e assim por diante.

Neste post, nós revelamos alguns dos segredos do DRAM de 16 Kbit, um tipo de memória que marcou a história da informática e da eletrônica. Esperamos que você tenha gostado e aprendido algo novo.

Desvendando o DRAM de 16 Kbit

A memória DRAM (Dynamic Random Access Memory) é um tipo de memória volátil que usa capacitores para armazenar bits. Cada capacitor pode ser carregado ou descarregado, representando um bit 1 ou 0. O problema é que os capacitores vazam carga com o tempo, então eles precisam ser periodicamente recarregados para manter os dados. Esse processo é chamado de refresh, e é feito automaticamente pelo circuito do chip.

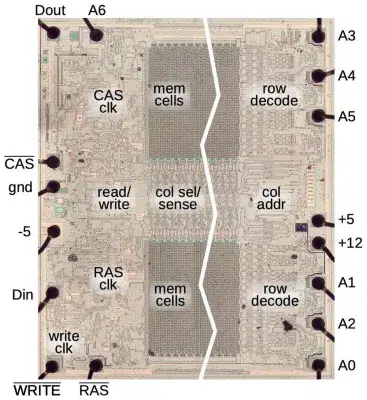

O chip 2117 tem uma capacidade de 16 Kbit, ou seja, 16384 bits. Ele é organizado em 256 linhas e 64 colunas, formando uma matriz de 16384 células de memória. Cada célula consiste em um transistor MOSFET e um capacitor, conectados como na figura abaixo.

Para acessar uma célula de memória, precisamos selecionar uma linha e uma coluna. Isso é feito usando dois registradores de endereço, um para a linha e outro para a coluna. O registrador de linha tem 8 bits e o registrador de coluna tem 6 bits, totalizando 14 bits de endereço. O chip tem 14 pinos de entrada para receber o endereço, mas eles são multiplexados, ou seja, usados duas vezes. Primeiro, enviamos os 8 bits da linha e ativamos o sinal RAS (Row Address Strobe). Depois, enviamos os 6 bits da coluna e ativamos o sinal CAS (Column Address Strobe). O chip então lê ou escreve o bit correspondente no pino de dados (D).

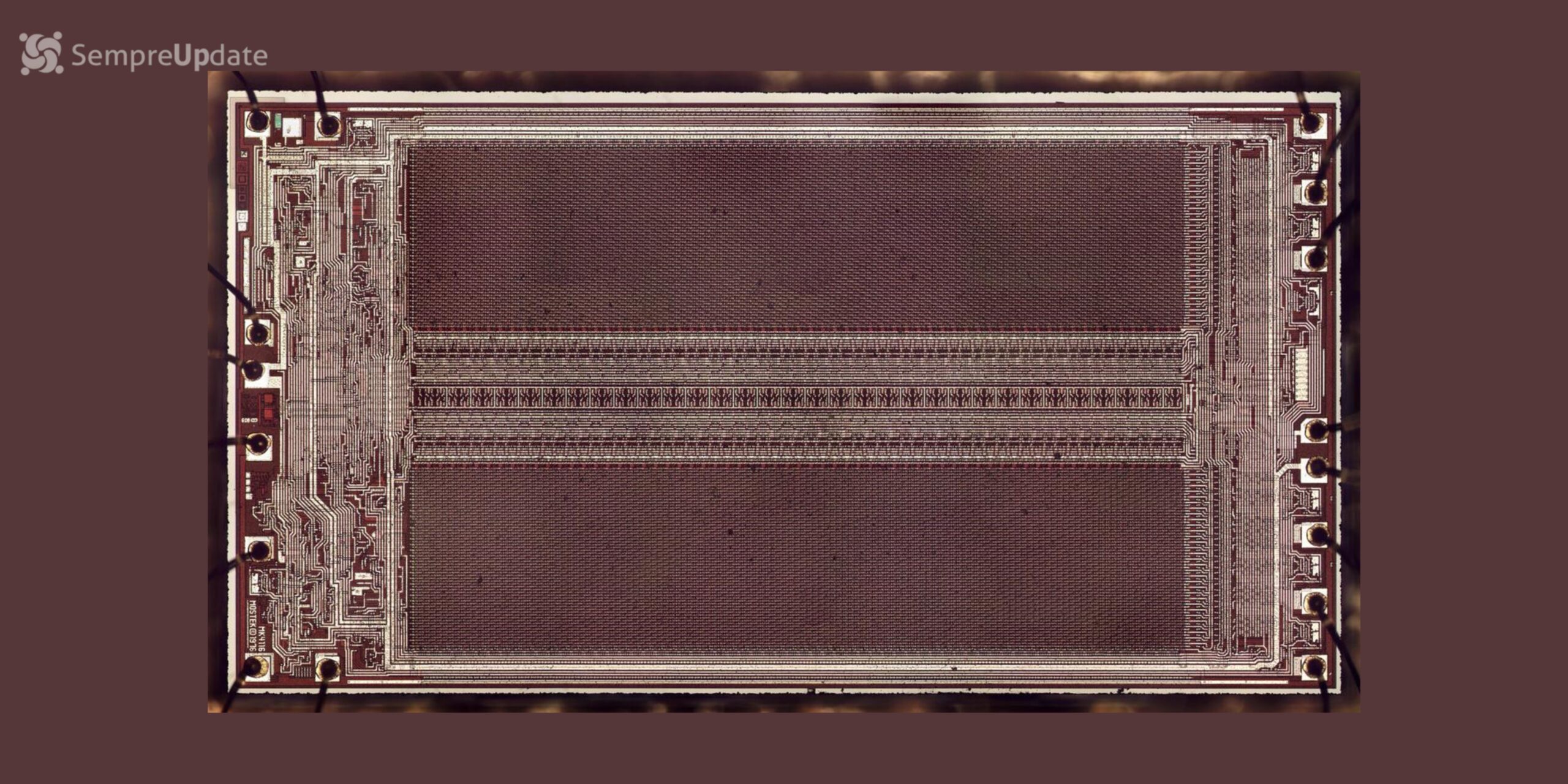

Agora que entendemos o funcionamento básico do chip, vamos ver como ele é por dentro. Para isso, usamos um microscópio eletrônico de varredura, que nos permite ver os detalhes da estrutura interna do chip. O MEV usa um feixe de elétrons para varrer a superfície do chip e gerar uma imagem com alto contraste e resolução.

Na imagem acima, podemos ver a parte superior do chip, onde estão os contatos metálicos que ligam os pinos externos aos circuitos internos. Cada contato tem um número que indica a função do pino correspondente. Por exemplo, o contato 1 é o pino Vcc (alimentação), o contato 8 é o pino RAS, o contato 14 é o pino D e assim por diante.

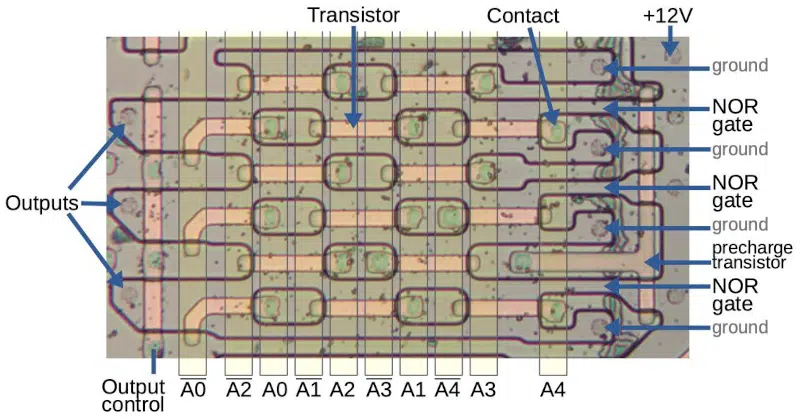

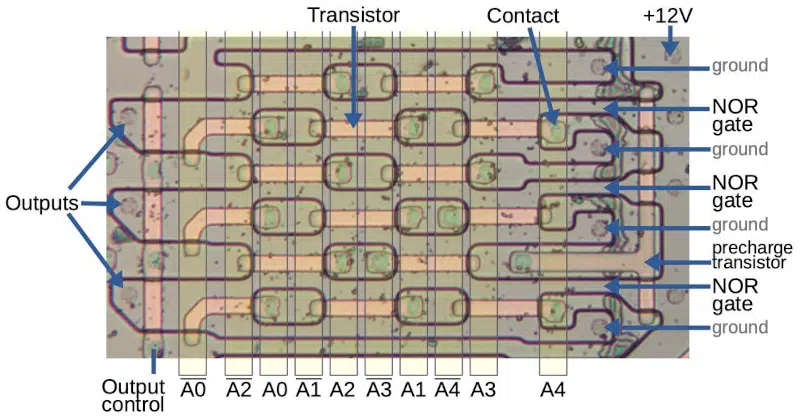

Se removermos a camada metálica do chip, podemos ver a camada de silício, onde estão os transistores e os capacitores que formam as células de memória. A imagem abaixo mostra uma parte da matriz de memória, com as linhas horizontais e as colunas verticais.

Cada interseção entre uma linha e uma coluna é uma célula de memória. Podemos ver o transistor MOSFET na forma de um retângulo escuro com três terminais: o gate (G), o source (S) e o drain (D). O capacitor está na forma de uma região circular clara logo acima do transistor. O terminal inferior do capacitor está conectado ao source do transistor, e o terminal superior está conectado a uma linha comum chamada Vbb (bias voltage).

Para entender melhor como o transistor e o capacitor funcionam juntos para armazenar um bit, vamos ampliar uma célula de memória e ver seus detalhes.

Na imagem acima, podemos ver que o transistor MOSFET é do tipo n-channel, ou seja, ele conduz corrente quando há uma tensão positiva no gate em relação ao source. O gate está conectado à linha de memória, o source está conectado ao capacitor e o drain está conectado à coluna de memória. O capacitor é formado por duas placas metálicas separadas por uma camada de óxido de silício, que é um isolante. A placa inferior é o source do transistor, e a placa superior é a linha Vbb.

Para escrever um bit 1 na célula, aplicamos uma tensão positiva na linha e na coluna correspondentes. Isso faz com que o transistor conduza e carregue o capacitor com a mesma tensão da linha. Para escrever um bit 0, aplicamos uma tensão zero na linha e na coluna. Isso faz com que o transistor corte e descarregue o capacitor.

Para ler um bit da célula, aplicamos uma tensão positiva na linha e uma tensão menor na coluna. Isso faz com que o transistor conduza parcialmente e transfira uma pequena carga do capacitor para a coluna. Essa carga é amplificada por um circuito chamado sense amplifier, que gera um sinal digital correspondente ao bit armazenado. O sense amplifier também recarrega o capacitor com a mesma tensão anterior, restaurando o bit que foi lido.

Esse processo de leitura é chamado de destrutivo, pois altera o estado do capacitor. Por isso, é necessário fazer o refresh da memória periodicamente, lendo todas as linhas e recarregando os capacitores. O chip 2117 tem um circuito interno que faz o refresh automaticamente a cada 2 milissegundos, usando um contador de 8 bits que percorre todas as linhas.

Neste post, vimos como funciona a memória DRAM de 16 Kbit usando o chip 2117 como exemplo. Vimos como o chip armazena bits em capacitores, como acessamos os bits usando linhas e colunas, e como o chip faz o refresh da memória. Também vimos imagens de microscópio eletrônico de varredura do chip, que nos revelaram os detalhes da estrutura interna do chip. Esperamos que você tenha gostado deste post e aprendido algo novo sobre a memória DRAM.