- A Atualização: O Kernel Linux 7.0 recebe uma reformulação massiva no subsistema CXL (Compute Express Link), fruto de um trabalho conjunto entre desenvolvedores da Intel e AMD.

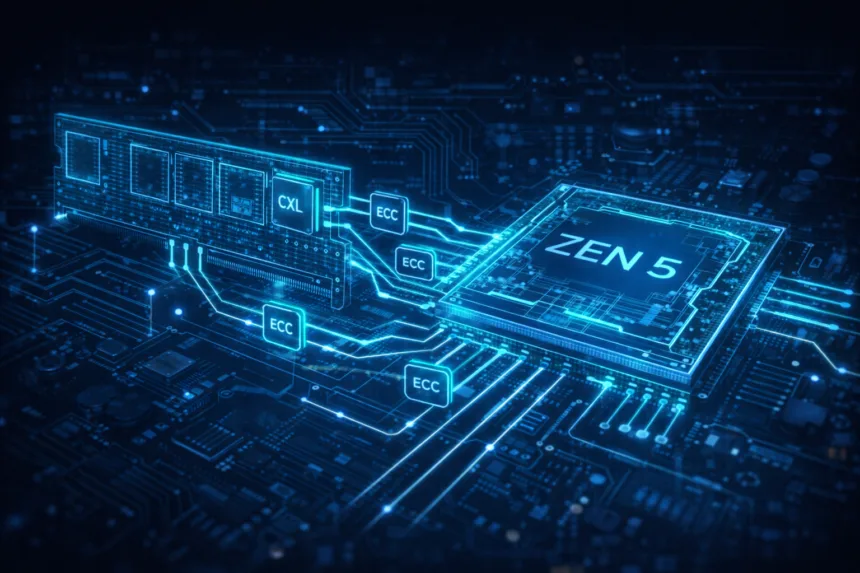

- Impacto nos Processadores AMD Zen 5: Na prática, o sistema operacional agora entende perfeitamente como a nova arquitetura da AMD mapeia a memória. O patch corrige falhas de alocação e garante que o Linux reconheça e use 100% da memória CXL disponível.

- Fim dos Travamentos por Falha de Memória: O tratamento de erros físicos (RAS) foi aprimorado. Se um módulo de memória CXL apresentar defeito, o Linux consegue isolar o problema apenas naquela porta, evitando que o servidor inteiro sofra um kernel panic e desligue.

- Preparação para Aceleradores: A mudança introduz o suporte base para dispositivos CXL Tipo 2. Isso permite que placas de rede inteligentes (SmartNICs) e GPUs compartilhem memória diretamente com a CPU de forma nativa e sem gargalos.

- Disponibilidade: O código já foi aprovado por Linus Torvalds e chega com o lançamento da versão estável do Linux 7.0, impactando diretamente a estabilidade e a performance do Linux em data centers e hipervisores corporativos.

O ecossistema de servidores e data centers está prestes a receber uma das atualizações estruturais mais densas dos últimos ciclos. Uma volumosa série de patches assinada por desenvolvedores da Intel e AMD, submetida por Dave Jiang e recentemente integrada por Linus Torvalds, promove uma reestruturação profunda no subsistema Compute Express Link (CXL) do Kernel Linux 7.0.

A mudança impacta diretamente a estabilidade corporativa e a topologia de memória, introduzindo o novo método cxl_memdev_attach para gerenciar alocações reservadas por software, abrindo caminho para aceleradores CXL Tipo 2 (Type 2 accelerators) e reescrevendo a arquitetura de relatórios de erro da porta CXL via PCI AER (Advanced Error Reporting). Além disso, o patch corrige gargalos de comunicação de memória na mais recente arquitetura da AMD, implementando a tradução de endereços via ACPI PRMT para a família de processadores Zen 5.

O que isso significa na prática:

Imagine que a placa-mãe do seu servidor é uma grande malha rodoviária e a memória RAM conectada via CXL é uma nova cidade recém-inaugurada. Até agora, se ocorresse um “acidente” (um erro de hardware ou falha de leitura) em uma das pontes (portas CXL), o Kernel Linux tinha dificuldades para relatar o problema de forma organizada, muitas vezes tratando o erro de forma isolada. Além disso, em processadores novos como o AMD Zen 5, a “cidade” usava um CEP diferente do padrão do sistema, fazendo o sistema operacional se perder ao tentar mapear a memória. A atualização cria um centro de controle unificado para gerenciar esses erros de via (RAS) e entrega um tradutor automático de CEPs (ACPI PRMT), garantindo que a CPU encontre e utilize a memória extra sem riscos de instabilidade ou perda de capacidade.

Detalhes da implementação: Subsistemas drivers/cxl, drivers/pci e arch/x86

A fusão de código (merge commit e812928be2ee1c27) não é uma simples adição de linhas. Com 50 arquivos modificados, mais de 2.500 inserções e cerca de 1.200 deleções, a arquitetura do driver CXL foi reorganizada para lidar com topologias corporativas complexas. O desenvolvedor propôs soluções definitivas para três pilares críticos da tecnologia CXL.

1. Tradução de endereços no AMD Zen 5

Em arquiteturas convencionais de hardware, o espaço de Endereço Físico do Host (HPA – Host Physical Address) é comum a todos os componentes do domínio do host. No entanto, o Data Fabric presente nas plataformas x86 da AMD (especificamente a família Zen 5) gerencia o acesso à memória física de forma segmentada. Dispositivos CXL podem ser configurados para usar “Endereços Normalizados”, que diferem dos Endereços Físicos do Sistema (SPA – System Physical Address).

Sem o patch, o Kernel Linux era incapaz de alinhar o HPA com o SPA em endpoints CXL operando em modo de endereçamento normalizado. Isso resultava em falhas na criação de regiões de memória e na incapacidade de aproveitar o hardware. A mudança implementa chamadas ao firmware via Platform Runtime Mechanism (ACPI PRM). O novo arquivo drivers/cxl/core/atl.c introduz o handler prm_cxl_dpa_spa_guid, que permite ao Kernel Linux interrogar a BIOS em tempo real para traduzir o Endereço Físico do Dispositivo (DPA) em um SPA compreensível pelo sistema operacional. O patch bloqueia modificações manuais nos decodificadores da AMD (CXL_DECODER_F_NORMALIZED_ADDRESSING), delegando a tradução exata aos metadados do firmware da placa-mãe.

2. Refatoração do RAS (Reliability, Availability, and Serviceability) e PCI AER

O segundo grande bloco técnico ataca o tratamento de erros do protocolo CXL. Anteriormente, a manipulação do Advanced Error Reporting (AER) tentava mapear e lidar com os erros diretamente nos dispositivos finais (endpoints). A mudança move todo o gerenciamento de registros de componentes para os objetos da hierarquia cxl_port.

O subsistema drivers/pci/pcie/aer.c foi expandido. A estrutura aer_err_info recebeu um novo bit de controle (is_cxl), diferenciando nativamente se uma anomalia transacional originou-se de um barramento PCI Express tradicional ou de uma via CXL. Erros recuperáveis e fatais agora sobem de forma coerente pela árvore de portas (Switch Downstream Ports para Upstream Ports e Root Ports), permitindo que o sistema isolem módulos de memória defeituosos sem derrubar o host (kernel panic), uma exigência crítica em hipervisores.

3. Aceleradores tipo 2 e intercalação MOD3

A infraestrutura adicionou a função cxl_memdev_attach, que altera radicalmente como os drivers de memdev funcionam no momento do boot. Ela obriga o driver do endpoint a se estabelecer de forma assíncrona antes de continuar a investigação de memória. Isso é o preâmbulo necessário para dispositivos CXL Tipo 2 — aceleradores (como placas de rede inteligentes ou GPUs) que possuem memória cache própria, mas precisam que ela mantenha coerência com a RAM principal da CPU.

Em conjunto, a atualização suporta a tradução de endereços para regiões de intercalação “MOD3” desalinhadas. Na prática, administradores podem criar arrays de memória combinando módulos de capacidades assimétricas ou rotas matemáticas complexas (como intercalação de vias 3, 6 ou 12), e a nova função genérica unaligned_dpa_to_hpa garante que a CPU não erre o bloco de destino durante a operação I/O.

Análise comparativa da estrutura CXL

| Recurso / Componente | Antes do patch | Depois do patch |

| Hierarquia de erros CXL | Mapeamento plano nos dispositivos finais (endpoints). Falhas estruturais podiam ser mal interpretadas pelo PCI AER. | Mapeamento focado na árvore cxl_port. Erros fluem hierarquicamente, garantindo isolamento de hardware e relatórios claros no dmesg. |

| Tradução AMD Zen 5 (HPA vs SPA) | Endereçamento normalizado quebrava a criação de partições de memória. Falha ao reconhecer módulos em certas pontes de host. | Integração com ACPI PRMT implementada. O Kernel Linux traduz ativamente DPA para SPA usando binários expostos pela BIOS. |

| Gerenciamento de soft reserved | Leitura engessada das tabelas EFI, atrapalhando a injeção de hardware a quente (hotplug) e criação dinâmica via DAX. | Função cxl_memdev_attach estabelece retenção e escalada limpa, suportando alocação complexa e hardware CXL Tipo 2. |

| Regiões desalinhadas (MOD3) | Kernel falhava ou apresentava regressão ao mapear partições que não fossem potências estritas de dois. | Algoritmo unaligned_dpa_to_hpa calcula remanescentes dinâmicos e alinha módulos 3, 6 e 12-way perfeitamente. |

Quando isso chega no meu PC?

O patch já ultrapassou as árvores de desenvolvimento e validações comunitárias, tendo sido fundido (merged) diretamente por Linus Torvalds na janela de integração (Merge Window) primária do kernel atual. Ele fará sua estreia oficial na versão estável do Kernel Linux 7.0, cuja liberação para o público geral está prevista para o final do segundo trimestre de 2026.

Para o usuário de servidores e estações de trabalho avançadas, o ganho será perceptível logo na atualização da sua distribuição. Distribuições com cadência ágil ou focadas em hardware recente, como Fedora Linux, Ubuntu (nas versões pós 26.04/26.10) e Arch Linux, começarão a compilar seus kernels padrão com estas bibliotecas CXL reescritas entre meados e o final de 2026. Em ambientes Enterprise, como Red Hat Enterprise Linux e SUSE, estes recursos podem ser transportados (backported) para versões corporativas ou ativados nativamente nos próximos ciclos de lançamento maiores. Profissionais que operam data centers com processadores AMD EPYC baseados em arquitetura Zen 5 verão o benefício dessa estabilidade imediatamente após o reboot na nova versão.