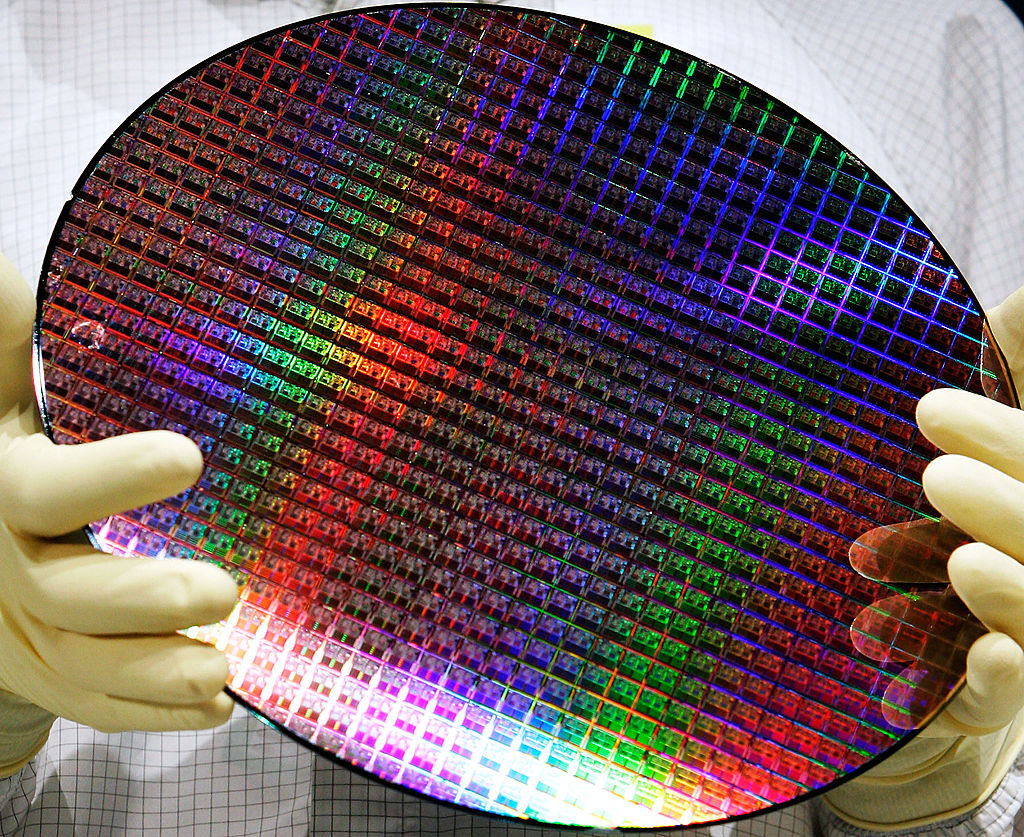

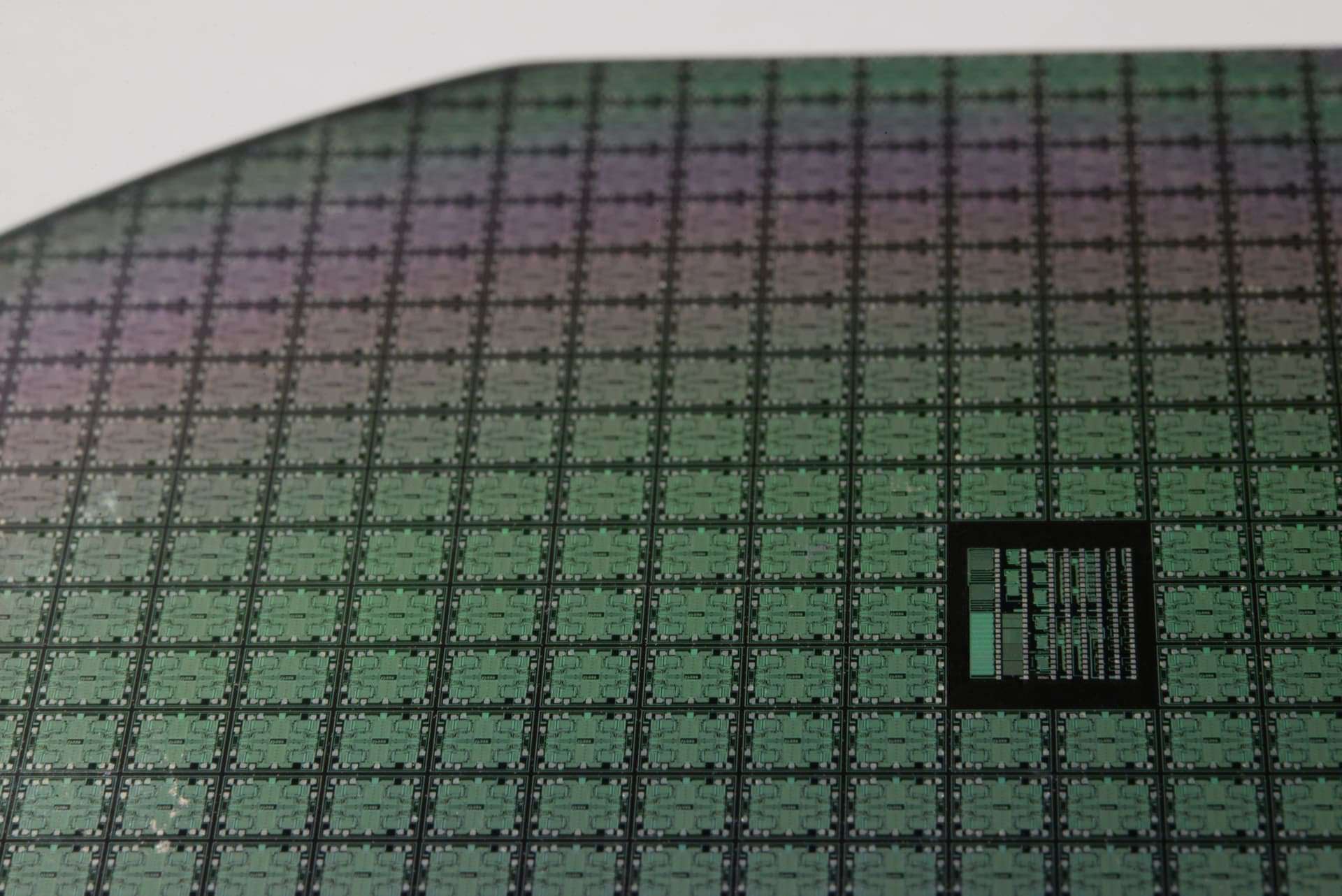

A TSMC compartilhou informações adicionais sobre seu próximo processo N3 de 3 nm. O processo N3 de 3 nm da TSMC (Taiwan Semiconductor Manufacturing Company) continuará a utilizar transistores FinFET em vez de mudar para algo como um design Gate-All-Around.

Em comparação com o N5, o N3 deve melhorar o desempenho em 10-15% e aumentar a eficiência energética em até 25-30%. Além disso, há uma melhoria de 1,7x na densidade lógica.

Processo de 3 nm da TSMC

De acordo com o roteiro da TSMC, o processo N3 entrará em produção de risco em 2021 antes de entrar em produção de volume em algum momento durante o segundo semestre de 2022. Nesse ínterim, os consumidores têm alguns outros processos pelos quais esperar.

O N5 deve ser usado na família do iPhone 12 da Apple, com lançamento previsto para o mês que vem. Uma otimização deste nó, o N5P, aumentará o desempenho em 5% e a eficiência energética em 10% em relação ao N5 padrão. Além disso, o N4 foi brevemente mencionado, com a produção de risco definida para começar em 2021 antes da produção de volume no ano seguinte.

Anteriormente, a TSMC revelou os indicadores técnicos do processo. Comparado com o de 5 nm, a densidade do de 3 nm é aumentada em 15%.

A TSMC produz em massa o processo de 7 nm há dois anos e este ano produzirá em massa o processo de 5 nm. Huawei e Apple já encomendaram a maior parte da capacidade de produção de 5 nm. Agora, o processo de 3 nm da TSMC também está dentro do cronograma.

A Samsung (rival da TSMC) anunciou que usará o GAA-FET e pulará os 4 nm e desenvolverá o de 3 nm em uma tentativa de acompanhar a TSMC.

Fonte: Tech Spot

Conheça o maior chip do mundo: 2,6 trilhões de transistores e 850.000 núcleos

Samsung encontra dificuldades em melhorar o rendimento de chips de 5 nm

Mediatek despachará mais de 80 milhões de chips 5G neste ano